- 您现在的位置:买卖IC网 > Sheet目录2008 > MAX11610EEE+T (Maxim Integrated Products)IC ADC SERIAL 10BIT 12CH 16-QSOP

MAX11606–MAX11611

Low-Power, 4-/8-/12-Channel, I2C,

10-Bit ADCs in Ultra-Small Packages

4

Maxim Integrated

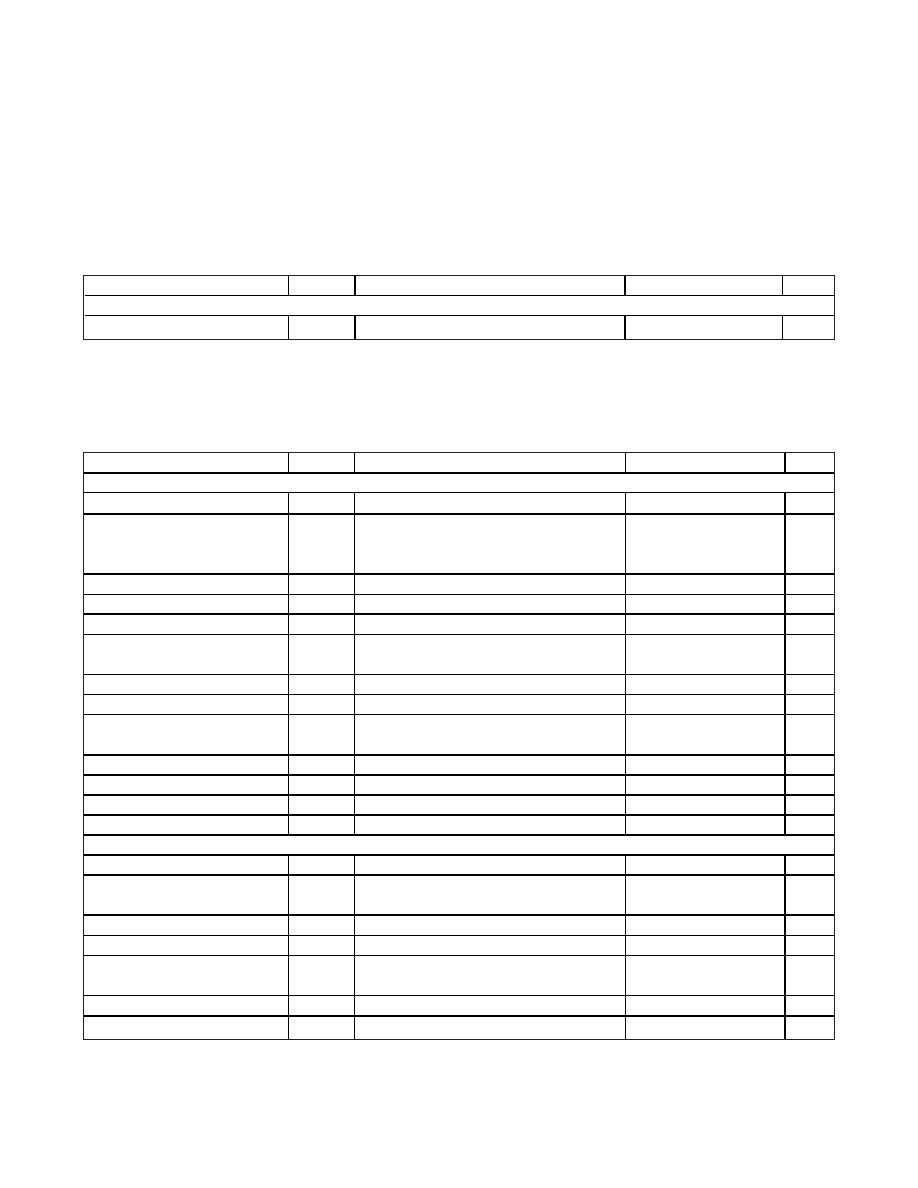

ELECTRICAL CHARACTERISTICS (continued)

(VDD = 2.7V to 3.6V (MAX11607/MAX11609/MAX11611), VDD = 4.5V to 5.5V (MAX11606/MAX11608/MAX11610), VREF = 2.048V

(MAX11607/MAX11609/MAX11611), VREF = 4.096V (MAX11606/MAX11608/MAX11610), fSCL = 1.7MHz, TA = TMIN to TMAX, unless other-

wise noted. Typical values are at TA = +25°C. See Tables 1–5 for programming notation.) (Note 1)

TIMING CHARACTERISTICS (Figure 1)

(VDD = 2.7V to 3.6V (MAX11607/MAX11609/MAX11611), VDD = 4.5V to 5.5V (MAX11606/MAX11608/MAX11610), VREF = 2.048V

(MAX11607/MAX11609/MAX11611), VREF = 4.096V (MAX11606/MAX11608/MAX11610), fSCL = 1.7MHz, TA = TMIN to TMAX, unless other-

wise noted. Typical values are at TA = +25°C. See Tables 1–5 for programming notation.) (Note 1)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

POWER REQUIREMENTS

Power-Supply Rejection Ratio

PSRR

Full-scale input (Note 10)

±0.01

±0.5

LSB/V

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

TIMING CHARACTERISTICS FOR FAST MODE

Serial-Clock Frequency

fSCL

400

kHz

Bus Free Time Between a

STOP (P) and a

START (S) Condition

tBUF

1.3

s

Hold Time for START (S) Condition

tHD,STA

0.6

s

Low Period of the SCL Clock

tLOW

1.3

s

High Period of the SCL Clock

tHIGH

0.6

s

Setup Time for a Repeated START

Condition (Sr)

tSU,STA

0.6

s

Data Hold Time

tHD,DAT

(Note 11)

0

900

ns

Data Setup Time

tSU,DAT

100

ns

Rise Time of Both SDA and SCL

Signals, Receiving

tR

Measured from 0.3VDD to 0.7VDD

20 + 0.1CB

300

ns

Fall Time of SDA Transmitting

tF

Measured from 0.3VDD to 0.7VDD (Note 12)

20 + 0.1CB

300

ns

Setup Time for STOP (P) Condition

tSU,STO

0.6

s

Capacitive Load for Each Bus Line

CB

400

pF

Pulse Width of Spike Suppressed

tSP

50

ns

TIMING CHARACTERISTICS FOR HIGH-SPEED MODE (CB = 400pF, Note 13)

Serial-Clock Frequency

fSCLH

(Note 14)

1.7

MHz

Hold Time, Repeated START

Condition (Sr)

tHD,STA

160

ns

Low Period of the SCL Clock

tLOW

320

ns

High Period of the SCL Clock

tHIGH

120

ns

Setup Time for a Repeated START

Condition (Sr)

tSU,STA

160

ns

Data Hold Time

tHD,DAT

(Note 11)

0

150

ns

Data Setup Time

tSU,DAT

10

ns

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MAX11616EEE+T

IC ADC SERIAL 12BIT 12CH 16-QSOP

MAX1162AEUB+T

IC ADC 16BIT 200KSPS 10-MSOP

MAX11637EEE+T

IC ADC 12BIT 8CH 16QSOP

MAX11643EEG+T

IC ADC 8BIT 8CH 24QSOP

MAX11645EUA+T

IC ADC 12BIT I2C/SRL 1CH 8UMAX

MAX11647EUA+T

IC ADC 10BIT I2C 94.4KSPS 8UMAX

MAX1166BEUP+

IC ADC 16BIT 165KSPS 20-TSSOP

MAX1168BCEG+

IC ADC 16BIT 200KSPS 24-QSOP

相关代理商/技术参数

MAX11611

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:2.7V to 3.6V and 4.5V to 5.5V, Low-Power, 4-/8-/12-Channel, 2-Wire Serial 10-Bit ADCs

MAX11611EEE+

功能描述:模数转换器 - ADC 10-Bit 12Ch 94.4sps 3.6V Precision ADC

RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX11611EEE+T

功能描述:模数转换器 - ADC 10-Bit 12Ch 94.4sps 3.6V Precision ADC

RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX11612

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Low-Power, 4-/8-/12-Channel, I2C, 12-Bit ADCs in Ultra-Small Packages

MAX11612_11

制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:Low-Power, 4-/8-/12-Channel, I2C, 12-Bit ADCs in Ultra-Small Packages

MAX11612DB+

功能描述:模数转换器 - ADC Integrated Circuits (ICs) Data Acquisition - Analog to Digital Converters - IC ADC 12BIT 4CH LP 8UMAX RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX11612EUA+

功能描述:模数转换器 - ADC 12-Bit 4Ch 94.4sps 5.5V Precision ADC

RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

MAX11612EUA+T

功能描述:模数转换器 - ADC 12-Bit 4Ch 94.4sps 5.5V Precision ADC RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32